摘 要:高清晰电视(HDTV)和无线通信网络的发展,对转换器速度和精度提出了更高的要求。基于新型传输门(TG) 结构组成的电流源单元矩阵和译码逻辑电路,提出一种适用于高清晰视频使用的高速8位CMOS电流舵数/模转换器(CS-DAC)。应用电流源单元矩阵结构和传输门结构的译码电路,有效减少了毛刺等干扰信号;TG结构设计的电路使晶体管数量和电路的延时显著减少;基于O.25 μm CMOS技术的DAC电路设计,功耗仅为21 mW,采样率达到1.5 GHz。仿真结果表明,电路的积分线性误差(INL)范围为-2~+2 LSB;微分线性误差(DNL)为-1~+4 LSB。

关键词:高速;数/模转换器;电流舵;CMOS

0 引 言

在信号采集处理、数字通信、自动检测和多媒体技术等领域,数/模转换器往往是不可缺少的部分。近年来,电子通信市场的快速发展,尤其是高清晰电视 (HDTV)和无线通信网络的开发应用,大大增加了对转换器速度和精度的要求。高清晰电视逐渐在人们的生活中普及,为了使HDTV得到更好的性能,就要有更高速和更高精度的DAC,因为高速更有利于减少图像闪烁和眼部疲劳,高精度可使图像更清晰。同时还要求设计的DAC面积小,功耗低。然而现在人们生活中常用的HDTV用DAC的分辨率一般为8位或者更高,采样率为500 MHz左右。这里介绍一个适用于HDTV应用的新型8位DAC,采样率达到1.5 GHz,功耗为21 mW。

在一般的数/模转换器的设计中,译码结构通常采用分段结构。在一般的设计中,为了减少延时,通常使用锁存器,同时配合复杂电流源结构,这种结构通常需要较大的能耗,并且采样率不是足够高。为了得到更高的采样率和更好的线性度,在此基于TG结构,设计了单位电流单元矩阵和译码器电路,同时采用简单的电流单元电路设计。

1 结构选择

在此,采用电流舵型DAC设计。这是因为电压型DAC所需元器件多,开关层数也较多,一般用于低速转换器内;电荷型DAC随精度的升高,面积急剧增大,而且对寄生电容敏感;电流型DAC具有高速的优势,但不适用于低压电路。电流舵型DAC是对电流型DAC的改进,常用于分段电路中。

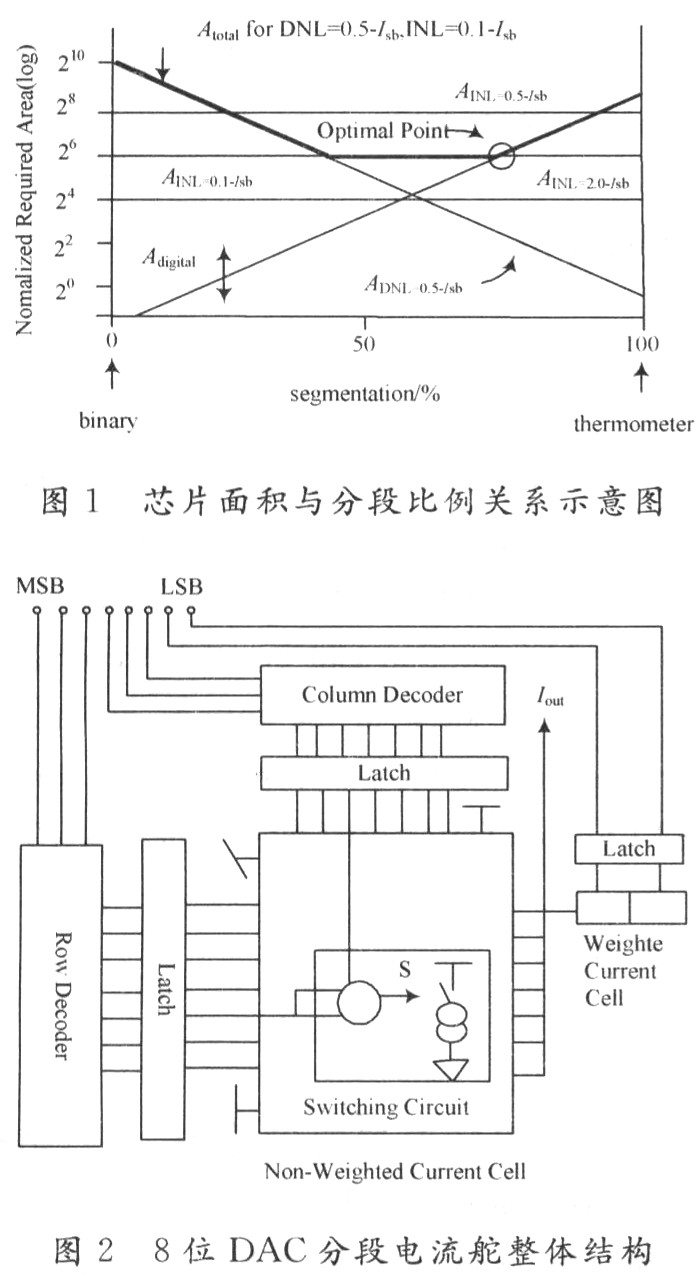

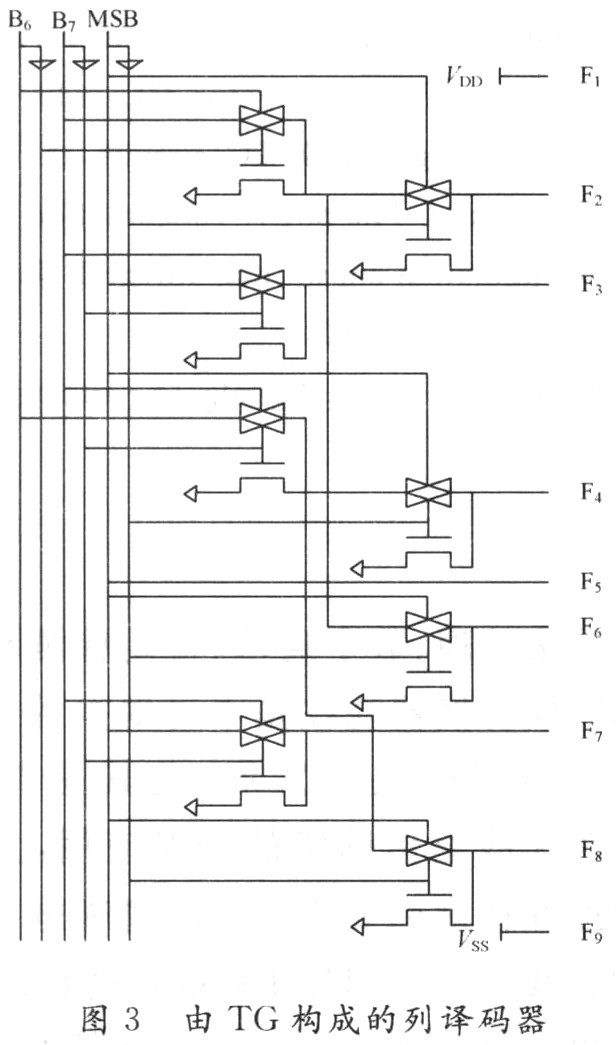

数/模转换器的译码方式一般分为二进制、温度计和分段式。温度计译码方式相对二进制译码方式,在减小DNL和INL方面有很大的优势,但是它的缺点是电路结构复杂。将二进制码和温度码结合起来,就产生了分段结构。在对匹配要求、高精度的高位采用温度计译码方式;低位采用二进制码方式,可以减少面积。这种分段结构既有二进制码结构简单的长处,又有温度码良好的线性特性。在这个设计中,提出使用电流源矩阵逻辑电路构成的高速8位DAC,根据Lin和Bult做了面积与分段比的关系图(见图1),为了在速度、分辨率、功耗、芯片面积、电路性能等多个方面得到一个折衷结果,分段的高6位采用温度计译码结构和低2位采用二进制译码结构。整个CS-DAC的结构如图2所示。

图2是一个说明8位分段式电流舵基本结构的例子。图中采用6+2分段结构,高6位数字信号通过行译码器(Rows Decoders)、列译码器(Columns Decod-ers)转换为温度计码,分别控制26-1=63个单位电流源,构成8×8电流源矩阵。多余的一个电流源作为Dummy器件,63个单位电流源和低2位二进制加权电流源的电流之和形成了阵列中整体电流源的电流。

2 译码逻辑电路

在DAC设计中,电流源单元、译码器和消除毛刺(噪声)结构是重要部分,DAC的性能由这些部分决定。为了改进在高频率动态线性,在此提出由传输门和晶体管组成组合逻辑译码电路。

2.1 传输门逻辑

因为NMOS管可以通过逻辑变量0传输,PMOS管可以通过逻辑变量1传输,用这两个MOS平行放置构成互补结构。在此,可以得到传输门(TG),并且对于TG,逻辑变量0,1都可以很好的传输。大家都知道,译码器之间的延迟时间是毛刺发生的主要原因,并且与全部使用CMOS逻辑电路比较,用TG设计的逻辑电路性能更好,延迟更小。经过验证,所有二输入逻辑门的可由传输门和反相器组成。作为一个事例,实现与非门逻辑,全部CMOS技术要求6只晶体管,但采用TG结构只需要5只晶体管。在内在DAC芯片上,它有两个信号,并且有翻转信号,因此没有反相器的需要,因而二只晶体管被减少。实验结果说明,芯片面积和功耗的大大减少了。

2.2 逻辑译码电路

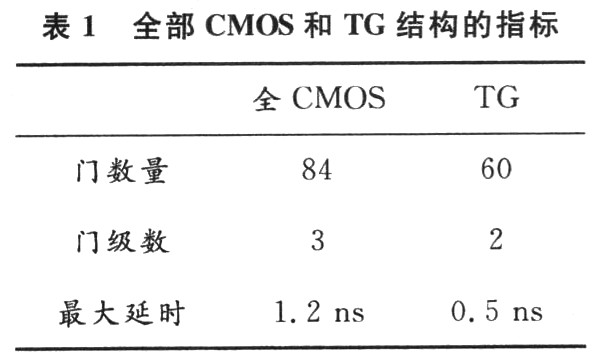

为减小功耗和减少延时,应该设计最少逻辑水平的行和列译码,运用TG逻辑电路组成3~8位行、列译码器。如此从高3位得到行译码器和从中间3位输入得到列译码器。运用TG的行译码器电路如图3所示。

行译码器结构与列译码器基本相同,但没有电源节点。使用TG逻辑译码器的另一巨大好处是可以减少晶体管的数量。在静态逻辑,参考文献[9]的译码器由84 只晶体管组成,但用TG结构组成的行和列译码器有30只晶体管,并且总数是60。这意味着芯片面积可能也被减少。较少的晶体管级数也帮助减少延时。另一方面,使用TG结构的逻辑门最大级数可减少到2级;不使用传输门结构的全CMOS结构的最高门级数是3,以上充分说明使用TG结构更有利减少延时和改进工作频率。表1给出相关的参量对比。

2.3 工作原理

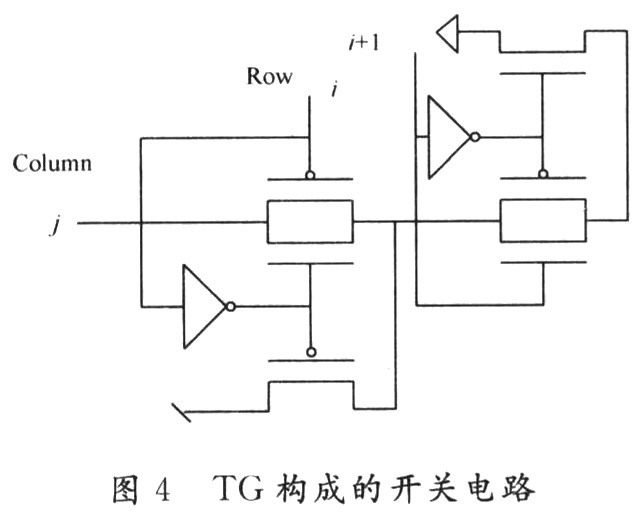

用行列译码器进行译码,单位电流源是导通还是截止,共有三种情况。第一种是所在行和下一行都是“1”,在这种情况下,无论列控制信号是否为“1”,该电流源均被选中。也就是说,对应的电流源开关状态为接通状态。第二种情况是所在的行控制信号为“1”,但是下一行的控制信号为“0”,这时,电流源是否被选中,要根据列控制信号来决定。如果列控制信号为“1”,则该电流源被选中;如果列控制信号为“0”,则该电流源不被选中,处于截止状态。第三种情况是所在行和下一行的控制信号均为“0”,那么不管其所在列的控制信号为多少,此电流源不会被选中,处于截止状态。TG构成的开关电路如图4所示。

3 电流源电路及减少毛刺电路

电流源电路是DAC的重要部分,同时为了减小毛刺反应,下面将介[FS:Page]绍减少毛刺的电路。

3.1 电流单元

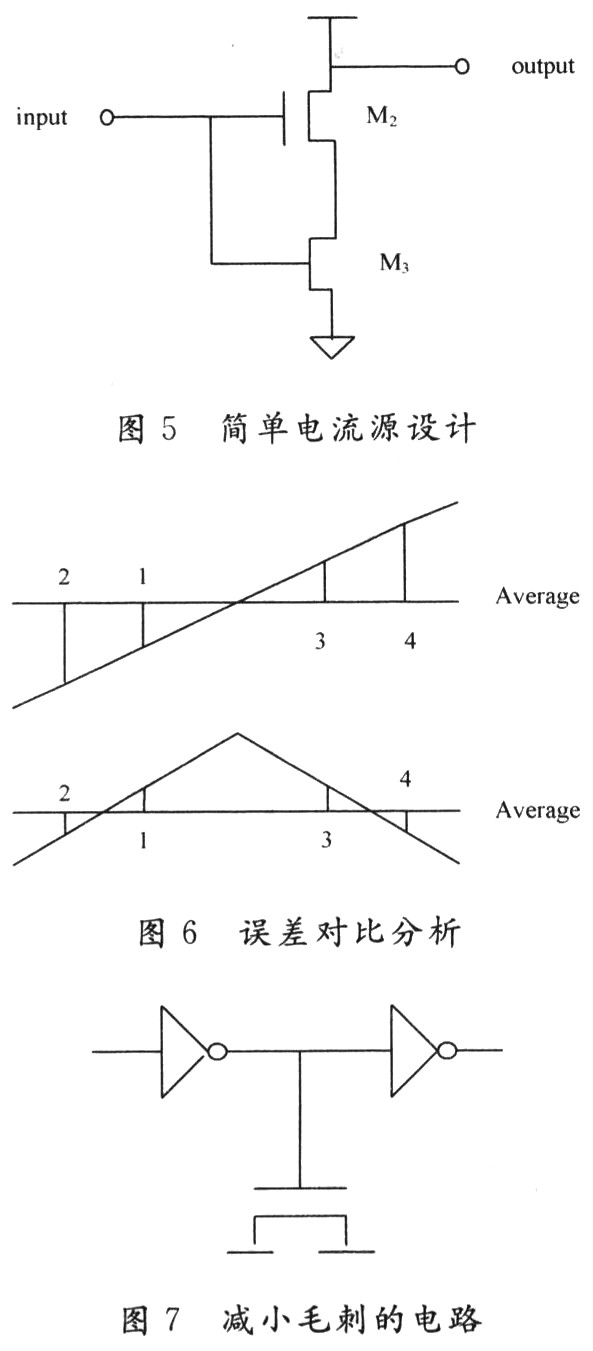

一般常用的设计均采用减少电路噪声和降低电流源的复杂结构。例如,差分电路、偏置电路、参考电流等需要很多数量的晶体管。在这个设计中,使用一个简单的电流单元结构,并且电流源采用由二只晶体管组成的电流源单元。与其他芯片相比,电路的面积可以大大减小,如图5所示。

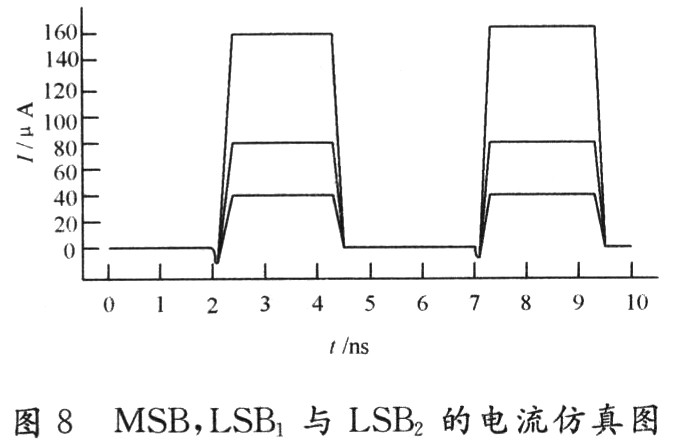

根据图6所示梯度误差与对称误差的对比,在单位电流源矩阵中采用层次式对称开关序列的布局,很好地减少了误差。

3.2 减少毛刺的电路

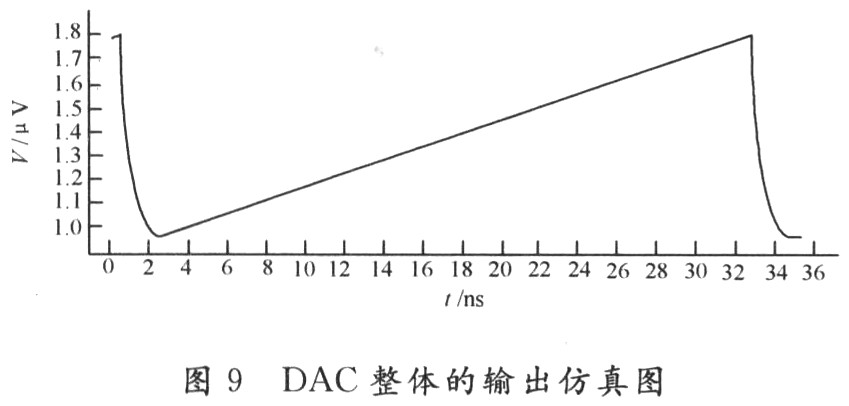

在基本的电流源单元,输出信号将是比较稳定的。在这个设计中电流源由开关电路输出信号控制,但输出信号不是足够的准确。因此,为了补偿这个缺点,同时改进电路的SNR,需要使用减少毛刺电路,如图7所示。

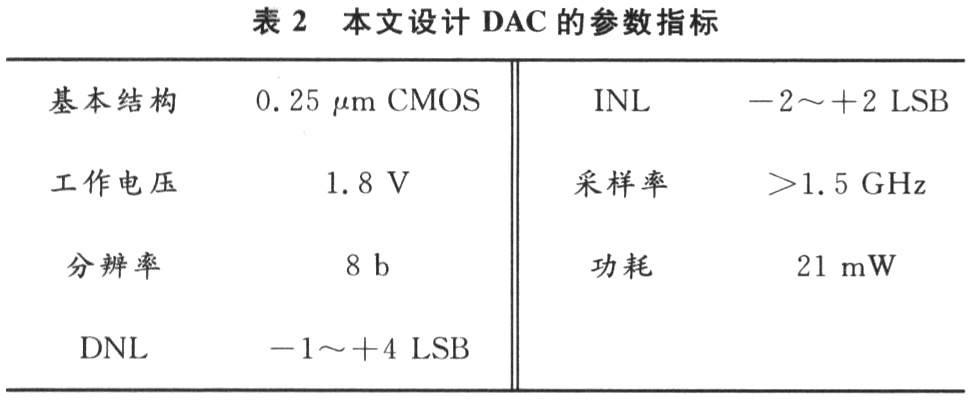

5 实验结果

该文设计的DAC基于O.25 μm CMOS技术,8位高速DAC适用于高清晰视频使用,并且使用TG晶体管和电路级数的数量可以明显减少,同时使用TG结构也可使电路延迟时间有效地减少,且毛刺也被大大减少。结果显示:这个设计可以达到1.5 GHz采样率和21 mW低功耗。

具体参数指标如表2所示。

6 结 语

本文提出基于新型传输门(TG)结构组成的电流源单元矩阵、译码逻辑电路和一种适用于高清晰视频使用的高速8位CMOS电流舵数/模转换器(CS- DAC)。应用电流源单元矩阵结构和传输门结构的译码电路能有效减少毛刺等干扰信号;采用TG结构设计的电路,可使晶体管数量和电路的延时显著减少;基于 0.25μmCMOS技术的DAC电路设计,功耗仅为21 mW,采样率达到1.5 GHz。仿真结果表明,电路的积分线性误差(INL)范围为-2~+2 LSB,微分线性误差(DNL)为-1~+4 LSB。

为您推荐

北京时间8月6日消息,据国外媒体报道,微处理器设计厂商MIPS技术试图使GoogleAndroid软件超越手机范畴,计划明年推出Android数字电视和机顶盒。尽管Android的开发初衷是作为智能手机操作系统,但计算机厂商很快将其用于上网本。今年6月已经有数家计算机厂商在台北国际电脑展上展示了Android上网本。现在,MIPS希望Android登陆家电产品。MIPS营销副总裁阿特-斯威夫特(ArtSwift)认为:“Android将大有用武之地。在我从事电子产业的25年中,从未见过哪项新技术能象Android这样迅速发展的,Android已快速超越了手机领域。”斯威夫特表示:“Androi

作者:李军博士中国科学院计算技术研究所高级工程师摘要:在文化振兴和三网融合背景下,探讨基于“服务互联”的融合型个人内容业务的服务模式以实现该服务模式的技术模型。关键词:个人内容业务服务互联文化振兴三网融合一、什么是“融合型个人内容业务”?文化是人类精神层面的一种积累,是能够教育和感化受众的,其终极目标是传承与认同,因此“文化是有力量的,是软实力的核心”。基于网络的内容服务包括文字阅读、影视节目、教育综艺与动漫游戏等,是文化传播的一种形式。在中国“文化振兴”与“三网融合”这个大背景下,网络内容服务能

随着社会信息量的增大,人们对多媒体视频压缩的要求越来越高,“高压缩、低比特速率”的高清视频压缩已广泛应用于家用电器、医疗设备、军事侦察、卫星遥感等领域。ADI公司最新推出的ADV212是一款具有实时压缩/解压缩标准(SD)视频信号和高清晰度(HDTV)视频信号功能的器件,具有可靠性好、配置灵活、支持视频格式多样等优点,适用于多种视频格式的数据处理。本文介绍了基于ADV212高清视频压缩系统的设计方案,该系统可支持SMPTE274M(1080i)视频实时编码。1ADV212的编解码原理图l所示为ADV212的功能图,主要由像素接口、小波变换引擎、熵编/解码器、嵌入式RISC处理器、存储器系统和内